Все модули оперативной памяти RAM имеют на борту чип SPD. Serial Presence Detect (SPD) — это стандартизированный способ доступа к информации о модуле памяти. Чтобы модуль памяти поддерживал SPD, стандарты JEDEC (комитет инженерной стандартизации полупроводниковой продукции) требуют, чтобы определенные параметры находились в младших 128 байтах микросхемы EEPROM, расположенной на модуле памяти. Эти байты содержат параметры модуля, такие как количество банков памяти и размерность чипов, настройки синхронизации, производителя, серийный номер и другую полезную информацию о модуле. Материнские платы, использующие память, автоматически определяют ключевые параметры модуля, считывая эту информацию. Например, данные SPD могут предоставить информацию о таймингах чипов памяти, на основании чего BIOS может автоматически настроить режим работы памяти. Также BIOS определяет размер планок памяти на основании информации из SPD (раньше он физически проверял объем памяти).

Так можно «показать» любой объем модуля памяти в BIOS, чем, кстати, иногда пользуются китайские производители поддельных или восстановленных модулей RAM. Они записывают прошивку с ложной информацией в чип, при этом сами чипы памяти могут не соответствовать.

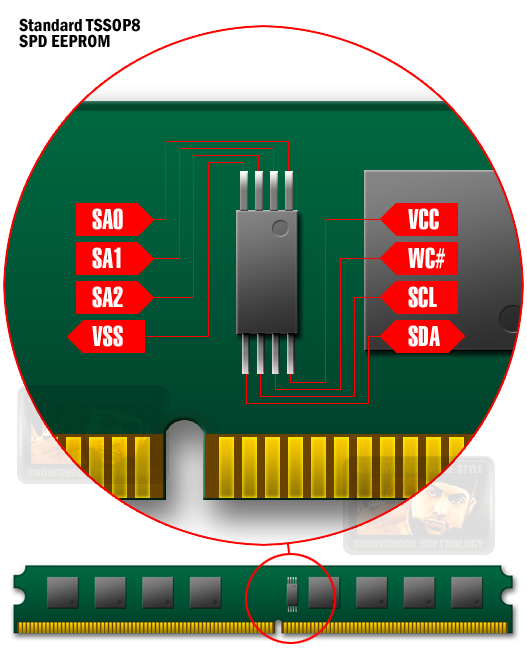

Сигналы чипов SPD

Доступ к встроенному программному обеспечению SPD EEPROM осуществляется с помощью шины SMBus, варианта протокола I²C. Это уменьшает количество коммуникационных контактов на модуле до двух: тактового сигнала SCL и сигнала данных SDA. 8 контактная микросхема EEPROM имеет общие контакты заземления с RAM, имеет собственный контакт питания VCC и три дополнительных контакта (SA0–2) для идентификации слота, которые используются для присвоения EEPROM уникального адреса в диапазоне 0x50–0x57 (поддерживается 8 слотов). Мало того, что линии связи могут быть разделены между 8 модулями памяти, один и тот же SMBus обычно используется на материнских платах для задач мониторинга состояния системы, таких как считывание напряжения питания, температуры процессора и скорости вращения вентилятора.

SPD EEPROM также реагирует на адреса шины I²C 0x30–0x37, если они не защищены от записи, а расширение (серия TSE) использует адреса 0x18–0x1F для доступа к дополнительному встроенному датчику температуры. Все эти значения представляют собой семибитные адреса I²C, образованные префиксом кода идентификатора типа устройства (DTIC) с SA0-2: для операции чтения (1100) из слота 3 используется 110 0011 = 0x33 (где 011 — это тройка, номер слота).

С последним битом чтения/записи он формирует 8-битный код выбора устройства. Обратите внимание, что семантика slot-id для операций защиты от записи отличается: для них они вообще не могут передаваться по контактам SA.

Начиная с DDR3 объем микросхемы увеличился до 256 Байт, в DRR4 — 384 байта, в DDR5 — уже 1 кБайт. Важно отметить, что DDR5 уже использует шину I3C, которая электрически обратно совместима с I2C.

DDR4, помимо стандартного диапазона адресов также использует два дополнительных адреса 0x36 (SPA0) и 0x37 (SPA1). Это потребовалось в связи с тем, что вместо стандартной микросхемы EEPROM AT24C02, теперь применена нестандартная типа EE1004, которая имеет две страницы, каждая по 256 байт. По адресам SPA0 и SPA1 теперь посылается команда для выбора активной страницы памяти, таким образом выполняется переключение банков памяти.

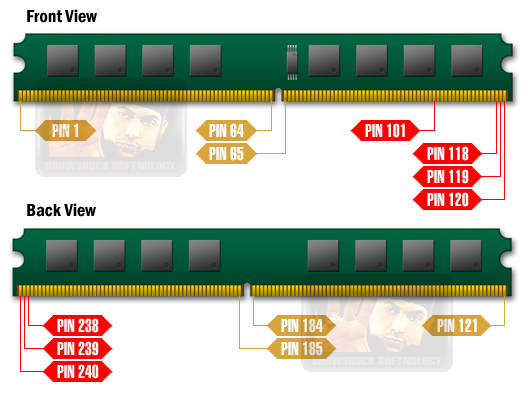

В самом слоте сигналы SPD выведены на слот DIMM — 4 в одном ряду, 3 в другом. Пример разводки для модуля DDR2:

| Сигнал | Номер пина | Описание сигнала |

| SA0 | 239 | Serial Device Address #0 |

| SA1 | 240 | Serial Device Address #1 |

| SA2 | 101 | Serial Device Address #2 |

| SCL | 120 | Serial Clock |

| SDA | 119 | Serial Data |

| VSSSPD (VSS) | 118 | Ground |

| VDDSPD (VCC) | 238 | Power Supply |

Содержимое SPD EEPROM

Содержимое SPD EEPROM

Для каждой ревизии SPD и, соответственно, стандарта DDR используется своя схема записи данных в чип, так как различаются объемы микросхем и количество доступных параметров. Вне зависимости от версии сначала идут байты данных, затем информация о модуле, затем тайминги и контрольная сумма CRC, после которых следует информация о производителе, серийный номер, дата производства и прочие специфичные для производителя данные.

Начиная с DDR3 для описания таймингов было введено введено понятие байта MTB (Medium Time Base). Этот байт определяет значение в пикосекундах, которое представляет собой фундаментальную базу времени для расчетов синхронизации с мелкой и средней зернистостью. Эти значения используются в качестве множителя для формулирования последующих параметров синхронизации (таймингов). Среднее базовое время (MTB) — 125 пс или 0,125 нс. В единицах MTB измеряются все остальные временные параметры.

Пример расчёта частоты памяти: режим 1600 МГц имеет цикл (период) 1250 пикосекунд, то есть 10 единиц MTB. Это значит, что в байте 18 для DDR4 для установки такого режима необходимо прописать 10 в 16-рицкой системе исчисления, то есть 0Ah.

Описание каждого из байтов DDR4 SPD приведено в этой статье. Из спецификации видно, что частота модуля задается в байтах 18 и 19, поддерживаемые тайминги памяти CAS Latency (CL) для разных режимов частот — с 20 по 23 байт, Minimum CAS Latency Time — 24 байт, Minimum RAS to CAS delay Time — 25, Minimum Row Precharge Delay Time — 26, Minimum Active to Precharge Delay Time — 28, Minimum Active to Active/Refresh Delay Time.

Описание байтов для других поколений SPD имеется в Wiki.

Важно помнить, что при изменении данных, необходимо пересчитать контрольную сумму. До DDR2 включительно она записывается в байт 63, в DDR3 в байты 126 и 127, а DDR4 в 126/127, 254/255, и 382/383, так как вся её память разделяется на 3 зоны, у каждой из которых своя контрольная сумма.

На ноутбуках на уровне BIOS включена защита от перезаписи всех 512 байтов SPD. Отключить ее можно, пропатчив BIOS. Проблема только в том, что пропатченные BIOSы в подавляющем большинстве отвергаются программами-прошивальщиками.

ПО для работы с SPD

В первую очередь, SPD надо научиться считывать. Это можно сделать как системными средствами, так и дополнительными утилитами.

В Windows данные модуля памяти можно получить через WMI запросы:

wmic memorychip list full |

В Linux для этого используется команда

sudo dmidecode -t memory |

или

sudo dmidecode --type 17 | more |

Для MacOS существуют портированные версии данной утилиты.

Для более удобного представления данных можно использовать утилиты AIDA64, CPU-Z.

Также для Linux существует утилита decode-dimms, которая позволяет удобно декодировать содержимое SPD или его дампа.

Редактирование SPD

Для редактирования содержимого можно вычитать микросхему на программаторе, так и воспользоваться утилитами, которые работают через шину памяти.

SPDTool an SPD-Z безнадежно устарели, поддерживают только модули памяти до DDR2 включительно.

Единственной живой на сегодня утилитой для конфигурирования SPD остается Thaiphoon Burner. Эта утилита поддерживает PC SDRAM, DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM, DDR5 SDRAM, LPDDR3 and LPDDR4. Бесплатная версия этой утилиты может считывать всю информацию, а также редактировать XMP профили, но не записывать их. Платная версия умеет все, включая интеграцию Intel XMP профилей.

Защита чипов от записи

SK Hynix, Samsung, Nanya Technology, Micron Technology, Crucial Technology и некоторые другие производители DIMM используют защиту от записи первых 128 байт SPD чипа EEPROM от перепрограммирования конечными пользователями. Они практикуют это ограничение в течение как минимум 5 лет, начиная с конца 2010 года, используя RSWP (обратимую защиту от записи программного обеспечения), которую нельзя удалить в среде Windows.

Кроме того, в 2013 году Intel выпустила контроллер-концентратор чипсетов 8-й серии с неприятным нововведением. Так называемый бит «SPD Write Disable» был введен, чтобы заставить хост-контроллер SMBus чипсета игнорировать команды записи по адресам 50h – 57h, связанным с SPD EEPROM. BIOS материнской платы устанавливает этот бит во включенное состояние при POST процедуре. Таким образом, весь массив SPD размером 256 байт 2-Кбитной микросхемы становится защищенным от записи. Этот бит отключения используется и во всех последующих чипсетах Intel.

Этот бит можно отключить через утилиту Thaiphoon Burner Professional version в чипсетах, старее 100-го семейства. Более подробно процесс описан автором.

Для того, чтобы разблокировать эту опцию на чипсетах семейства Intel 100, необходимо патчить BIOS через утилиту UEFITool.

Также интересно, что в платах некоторых вендоров, таких как ASUS, функцию SPD Write Disable можно отключить через BIOS.

Другой способ перепрограммировать микросхему EEPROM — через программатор. Чипы стандарта 24C02 можно подключить даже к дешевому программатору CH341, но с добавлением конденсатора на 0,15 мкФ по питанию (между 4 и 8 ножками).

[Посещений: 3 707, из них сегодня: 1]

[Посещений: 3 707, из них сегодня: 1]